Research

Research

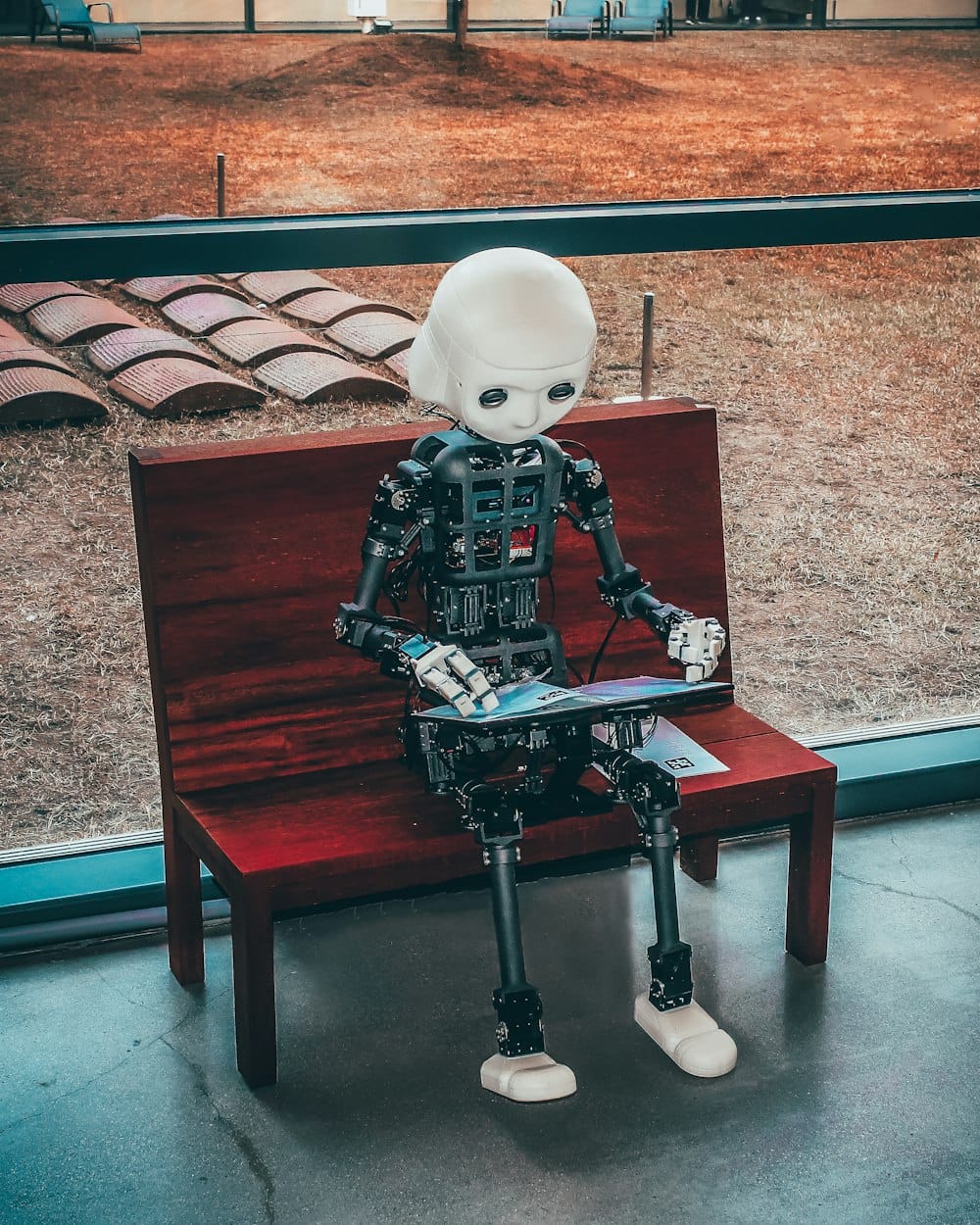

Wildcat: Educational RISC-V Microprocessors

Abstract

The paper "Wildcat" challenges the traditional 5-stage pipeline model used in computer architecture education by examining simpler RISC-V organizations for teaching and implementation. Analysis across FPGA and SkyWater130 ASIC designs

Research

Evaluating IOMMU-Based Shared Virtual Addressing for RISC-V Embedded Heterogeneous SoCs

Abstract

This work quantitatively evaluates Input-Output Memory Management Unit (IOMMU)-based Shared Virtual Addressing (SVA) for RISC-V embedded heterogeneous SoCs, enabling zero-copy data offloading between host and accelerator. While IO address translation introduces

🔒 Members

Research

What’s on tap from RISC-V in 2025? - Jon Peddie Research

Abstract

The analysis from Jon Peddie Research forecasts the critical trends and commercial trajectory of the RISC-V architecture expected throughout 2025. It predicts a significant push beyond embedded systems, focusing on higher-performance segments

Research

What’s on tap from RISC-V in 2025? - Jon Peddie

Abstract

The analysis by Jon Peddie forecasts the significant technological advancements and market shifts anticipated within the RISC-V ecosystem through 2025. The article highlights the architecture's accelerated push into mainstream computing,

Research

Translating Common Security Assertions Across Processor Designs: A RISC-V Case Study

Abstract

This work introduces a novel methodology for translating pre-defined security assertions across disparate processor architectures, addressing the high cost and complexity of manual verification, especially within the growing RISC-V ecosystem. The automated

Research

A Novel Approach to Reducing Testing Costs and Minimizing Defect Escapes Using Dynamic Neighborhood Range and Shapley Values

Abstract

This article presents a novel verification methodology aimed at substantially reducing hardware testing costs while simultaneously minimizing defect escapes. The approach integrates Dynamic Neighborhood Range (DNR) algorithms for efficient adaptive test generation