Research

Research

PermuteV: A Performant Side-channel-Resistant RISC-V Core Securing Edge AI Inference

Abstract

PermuteV is a performant side-channel resistant RISC-V core designed to secure Edge AI inference models against physical attacks, which frequently expose confidential neural network data. The core employs a novel hardware-accelerated defense

Research

A Brief History of Formal Methods in China

Abstract

This article details the historical trajectory and evolution of formal methods (FM) research and practical application within the technological landscape of China. It chronicles key academic milestones, influential research institutions, and major

Research

ChatArch: A Knowledge-driven Graph-of-thought LLM Framework for Processor Architecture Optimization

Abstract

ChatArch introduces a novel Knowledge-driven Graph-of-thought (GoT) LLM framework designed to automate and optimize the challenging process of processor architecture design. By integrating domain-specific knowledge graphs, ChatArch facilitates structured, multi-path reasoning for

Research

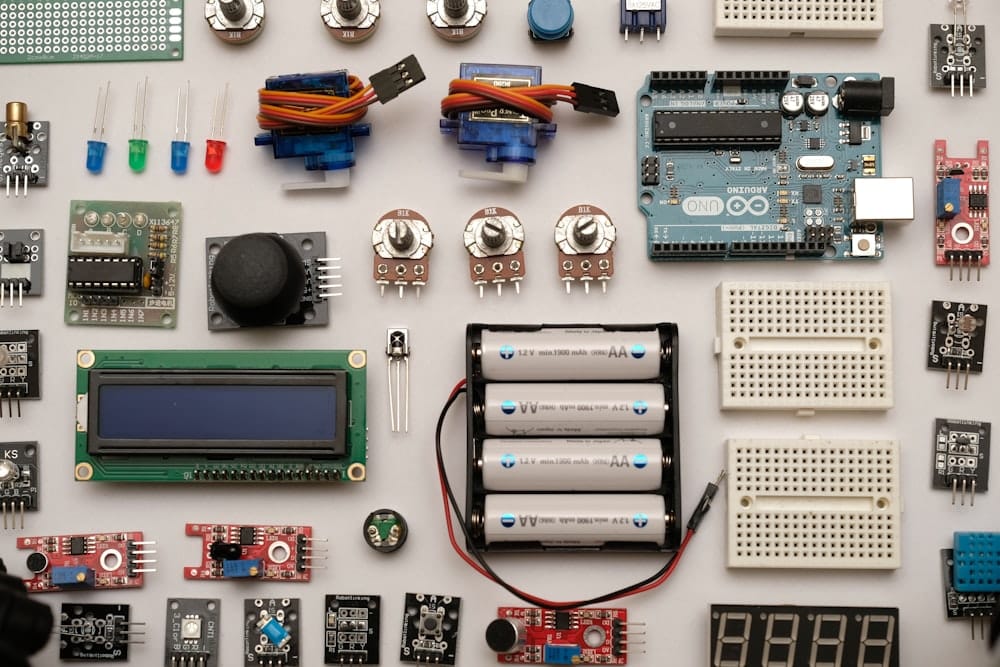

Quantum-Resistant FOTA: End-to-End Decentralized Firmware Updates for IoT Using Blockchain and CRYSTALS-Dilithium

Abstract

This paper presents a novel, quantum-resistant (QR) firmware update architecture designed to secure the critical Firmware Over-The-Air (FOTA) process for resource-constrained IoT devices. The system achieves end-to-end decentralization and integrity by leveraging

Research

Design of a USB RAID Controller for ARM SBC cluster server

Abstract

This paper presents the design and implementation of a novel USB RAID controller specifically engineered for ARM Single Board Computer (SBC) cluster servers. The innovation addresses significant storage and redundancy limitations inherent

Research

Towards high scalability and fine-grained parallelism on distributed HPC platforms

Abstract

Distributed High-Performance Computing (HPC) platforms face significant challenges in achieving simultaneous high scalability and fine-grained parallelism due to communication and synchronization overhead. This paper introduces a novel architecture and runtime co-design approach