🔒 Members

News

Qualcomm’s Ventana acquisition points to a long-term RISC-V strategy to complement its Arm lineup - Tom's Hardware

Abstract

Qualcomm's acquisition of Ventana Micro Systems signifies a substantial, long-term commitment to developing the RISC-V architecture. This strategic investment is designed to complement Qualcomm's existing dominance in the

News

VEGA AS2161 “DHRUV64” – A 1GHz dual-core 64-bit RISC-V microprocessor designed in India - CNX Software

Abstract

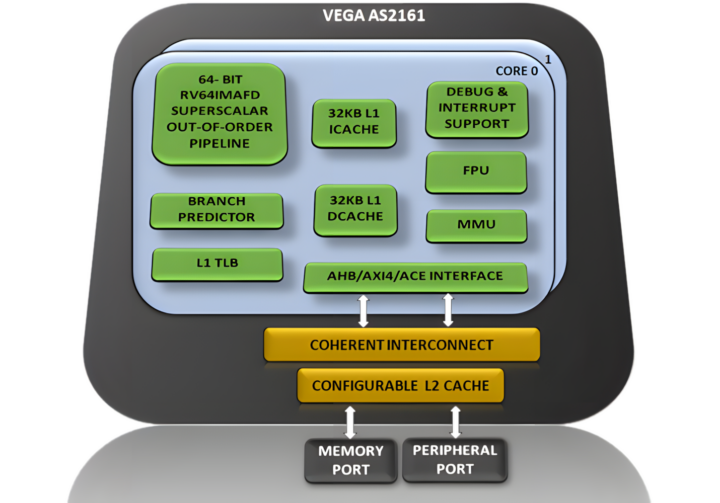

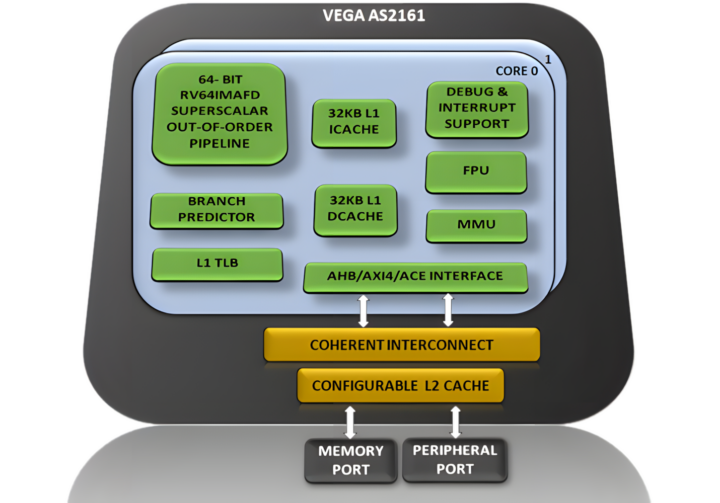

The VEGA AS2161, marketed as the “DHRUV64,” is a significant new development in the RISC-V ecosystem, featuring a 64-bit, dual-core microprocessor architecture. Operating at a respectable 1 GHz clock speed, this chip

News

Qualcomm’s Ventana acquisition points to a long-term RISC-V strategy to complement its Arm lineup - Tom's Hardware

Originally published on Google News - RISC-V

Qualcomm’s Ventana acquisition points to a long-term RISC-V strategy to complement its Arm lineup Tom's Hardware

AI Analysis

Key Highlights

* Major Acquisition: Qualcomm

News

LilyGo T-Display P4 handheld has an ESP32-P4 RISC-V processor and a 4.1 inch display - Liliputing

Abstract

LilyGo has introduced the T-Display P4 handheld, a new development device integrating Espressif's powerful ESP32-P4 RISC-V processor. This handheld features a 4.1-inch display, making it suitable for portable interface

Embedded

VEGA AS2161 “DHRUV64” – A 1GHz dual-core 64-bit RISC-V microprocessor designed in India

Abstract

The Government of India has launched the DHRUV64 (VEGA AS2161), an indigenous dual-core 64-bit RISC-V microprocessor developed by C-DAC, marking a significant progression in the country's semiconductor efforts. Clocked at

Research

Toward Comprehensive Design Space Exploration on Heterogeneous Multi-core Processors

Abstract

Designing optimal heterogeneous multi-core processors requires navigating an exponentially large Design Space Exploration (DSE) covering core mixes, interconnects, and scheduling policies. This paper introduces a novel, comprehensive DSE framework specifically tailored for

Research

TEMpesT: Testing Empirically for Memory Transistency

Abstract

TEMpesT is a novel empirical testing methodology designed to rigorously verify memory transistency behaviors in modern CPU implementations, specifically targeting the complexities of the RISC-V Weak Memory Ordering (RVWMO) model. The system