Research

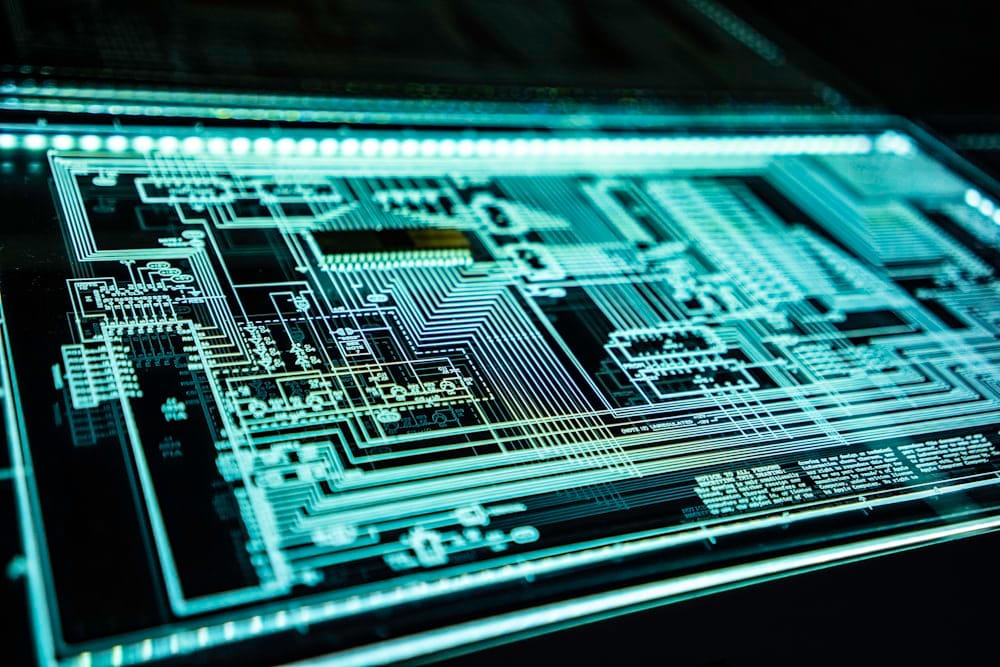

Tool for checking complex computer architectures reveals flaws in emerging design - Princeton University

Abstract

Princeton University researchers developed a novel formal verification tool designed to check the integrity and specification correctness of complex computer architectures. When applied to an emerging chip design, the tool successfully uncovered

Research

Epiphany-V: A 1024 processor 64-bit RISC System-On-Chip

Abstract

The Epiphany-V project details the design of a highly parallel System-On-Chip featuring 1024 64-bit RISC processors fabricated using 16nm FinFET technology. This massively multi-core architecture integrates 64MB of on-chip SRAM and utilizes

Research

Colombia designs 32-bit MCU based on RISC-V - EE Times Asia

Originally published on Google News - RISC-V Research

Colombia designs 32-bit MCU based on RISC-V EE Times Asia

Research

A near-threshold RISC-V core with DSP extensions for scalable IoT Endpoint Devices

Abstract

This paper presents the design of an open-source RISC-V processor core optimized for Near-Threshold (NT) operation within scalable multi-core clusters targeting energy-constrained IoT endpoint devices. The core integrates instruction extensions for Digital

Research

TriCheck: Memory Model Verification at the Trisection of Software, Hardware, and ISA

Abstract

Memory Consistency Models (MCMs) are typically verified in isolation across the hardware-software stack, leading to unverified interactions between compilers, ISA, and hardware implementations. TriCheck is a novel toolflow designed for full-stack MCM

Research

The Renewed Case for the Reduced Instruction Set Computer: Avoiding ISA Bloat with Macro-Op Fusion for RISC-V

Abstract

This paper renews the argument for Reduced Instruction Set Computers (RISC), demonstrating that the open RISC-V ISA, particularly its compressed variant (RV64GC), can achieve performance and code density superior to complex proprietary