VEGA AS2161 “DHRUV64” – A 1GHz dual-core 64-bit RISC-V microprocessor designed in India

Abstract

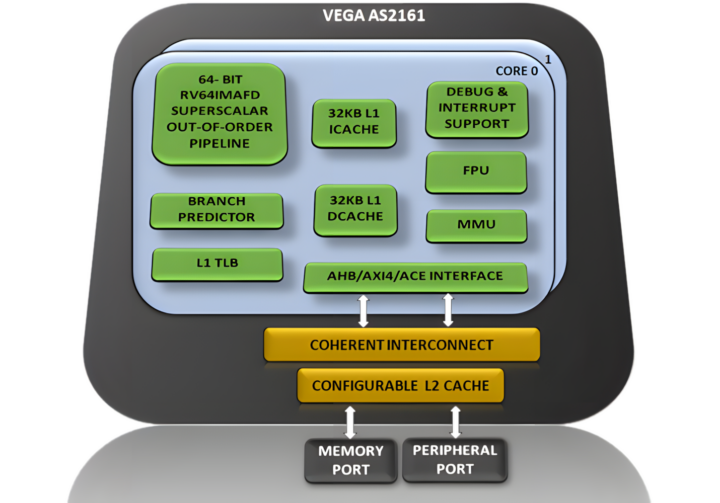

The Government of India has launched the DHRUV64 (VEGA AS2161), an indigenous dual-core 64-bit RISC-V microprocessor developed by C-DAC, marking a significant progression in the country's semiconductor efforts. Clocked at 1 GHz, this MPU features the RV64IMAFD instruction set and supports Linux, positioning it for higher-performance applications. Its architecture utilizes an advanced 13-16 stage out-of-order pipeline and sophisticated branch prediction mechanisms.

Report

Key Highlights

- Product Name/Model: DHRUV64 (VEGA AS2161).

- Designer: Centre for Development of Advanced Computing (C-DAC) under the Microprocessor Development Programme (MDP).

- Core Configuration: Dual-core, 64-bit MPU.

- Performance: Clocked at 1 GHz.

- Software Capability: Supports the Linux operating system.

- Context: Represents a significant step forward from earlier indigenous designs like SHAKTI, AJIT, and the initial VEGA processors (THEJAS32/THEJAS64).

Technical Details

- Instruction Set Architecture (ISA): RISC-V 64G (RV64IMAFD).

- Pipeline Implementation: Advanced 13-16 stage out-of-order implementation.

- Core Architecture: Utilizes a Harvard architecture with separate instruction and data paths.

- Branch Prediction: Features an advanced branch predictor incorporating BTB (Branch Target Buffer), BHT (Branch History Table), and RAS (Return Address Stack).

Implications

- Technological Sovereignty: The DHRUV64 is heralded as a “fully indigenous microprocessor,” directly supporting India's goal of self-reliance and boosting its domestic semiconductor design industry.

- Performance and Complexity: Moving to a 1 GHz dual-core, 64-bit core with an out-of-order pipeline signifies a substantial leap in performance and architectural complexity compared to C-DAC's previous VEGA cores.

- Ecosystem Viability: Achieving 1 GHz clock speed and native Linux support makes the VEGA AS2161 viable for a wider range of high-performance embedded systems and potentially entry-level computing tasks, further solidifying the RISC-V ecosystem within India.

Technical Deep Dive Available

This public summary covers the essentials. The Full Report contains exclusive architectural diagrams, performance audits, and deep-dive technical analysis reserved for our members.